# OPTICAL ELEMENT AND OPTICAL BUS, AND OPTICAL INTERPROCESSOR COUPLED NETWORK USING THEM

Patent number:

JP5152608

**Publication date:**

1993-06-18

Inventor:

BABA SHINICHI; NAKAMURA MASARU; KOYANAGI SHIGERU; TANABE NOBORU; SEKIDO KAZUNORI;

**UENISHI KATSUJI**

**Applicant:**

TOKYO SHIBAURA ELECTRIC CO

Classification:

- international:

H01L31/12; H01L33/00; H04B10/02; H04Q11/00; H01L31/12; H01L33/00; H04B10/02; H04Q11/00;

(IPC1-7): H01L31/12; H01L33/00; H04B10/02

- european:

H04Q11/00P1

Application number: JP19910291646 19911107

Priority number(s): JP19910291646 19911107; JP19910159209 19910629;

JP19910252631 19910930

Report a data error he

Also published as:

US5488735 (A

#### Abstract of JP5152608

PURPOSE: To obtain an optical interprocessor coupled network capable of high-speed connective switching, by providing a substrate, a light emitting element provided therein, and a concentric- type light receiving element surrounding it. CONSTITUTION: A light receiving element 53 surrounds the periphery of a light emitting and transmitting element 52 in the central part of a semiconductor substrate 51, and the light receiving element 53 converts an incident light from its bottom surface into the electrical signal to emit a light from the top surface of the light emitting and transmitting element 52. The central part comprises a multilaver structure, and therein, has an active layer 54, and the upper and lower layers 55a, 55b thereof are controlled to perform light emitting and receiving functions. The concentrictype light receiving element 53 having a multilayer photodiode structure too can be provided with an electrode in its uppermost layer, and has the wide light receiving range for 100mum in each direction, and a diffracted light having a wide emitting angle is emitted from an outgoing port. Therefore, by constituting an optical bus using the device comprising the light emitting/receiving elements arrayed in the form of a matrix and making an inter-substrate transferring frequency high using an integration and increasing the number of inter-substrate wirings to increase the number of connective substrates, the highly dense configuration of a coupled network is made possible.

Data supplied from the esp@cenet database - Worldwide

#### (19)日本国特許庁(JP)

## (12)公開特許公報 (A)

(11)特許出願公開番号

### 特開平5-152608

(43)公開日 平成5年(1993)6月18日

(51) Int. Cl. s

識別記号

FΙ

H01L 33/00

H 8934-4M

31/12

G 7210-4M

H04B 10/02

8426-5K

H04B 9/00

T

審査請求 未請求 請求項の数7

(全24頁)

(21)出願番号

特願平3-291646

(22)出願日

平成3年(1991)11月7日

(31)優先権主張番号 特願平3-159209

(32)優先日

平3(1991)6月29日

(33)優先権主張国

日本(JP)

(31)優先権主張番号 特願平3-252631

(32)優先日

平3(1991)9月30日

(33)優先権主張国

日本(JP)

(71)出願人 000003078

株式会社東芝

神奈川県川崎市幸区堀川町72番地

(72)発明者 馬場 伸一

神奈川県川崎市幸区小向東芝町1 株式会

社東芝総合研究所内

(72)発明者 中村 優

神奈川県川崎市幸区小向東芝町1 株式会

社東芝総合研究所内

(72)発明者 小柳 滋

神奈川県川崎市幸区小向東芝町1 株式会

社東芝総合研究所内

(74)代理人 弁理士 三好 秀和 (外4名)

最終頁に続く

#### (54) 【発明の名称】光素子および光バス、およびこれらを用いた光学式プロセツサ間結合網

#### (57)【要約】

【目的】 光学的並列プロセッサ間結合バスと光デバイ ス結合網の構築。

垂直に基板を貫く光ビーム束で構成し、光の 曲折点に配したレンズでピームを絞り、基板の両端を光 ファイバーアレイで接続する並列リングパスで制御メモ リ内の調停済み結合パターンによる切換が可能。送信、 中継、受信素子群中には機能を兼ね、増幅機能を有すデ ータ受信、中継素子を備え、複数の受光ビームからビー ムを選択し、位置送信制御側プロセッサに対応させる光 素子構成された並列光リングバス。複数の受信素子の下 に帯状受光素子、導波路型集約器を配し、導波路、レン ズ、フィイバーを光セル位置に対応接置構成光デバイ ス。

基板間配線制御を大幅に緩和し、クロスバ・ スイッチに近いプロセッサ間の密な結合と高い転送速度 を有す並列計算機プロセッサ間結合網を構築。

【特許請求の範囲】

【請求項1】 基板と、

この基板に設けられた発光素子と、

前記基板の発光素子の周囲に設けられた同心円状の発光 素子と、

1

を具備したことを特徴とする光素子。

【請求項2】 複数のボード間を光信号によって通信するための光パスであって、

前記複数のボードにマトリクス状に配置され、光信号の 送受信を行う複数の光素子と、

他のポードから送信された光信号を前記光素子を介して 受信した自己のポードに取り込む受信部と、

自己のポードで発生した信号を前記光素子を介して他の ポードへ送信する送信部とを具備することを特徴とする 光バス。

【請求項3】 前記光素子は受光素子と発光素子とを具備し、

前記マトリクス状各行の前記受光素子を前記ボード上の複数のマイクロプロセッサの入力端子に対応付けて接続し、前記マトリクス状各列の前記発光素子を前記マイク 20 ロプロセッサの出力端子に対応付けて接続し、前記各ボード上の複数のプロセッサ間で通信するようにした請求項4記載の光バス。

【請求項4】 表面で受光した光信号を裏面から出力可能な光デバイスを有する複数の基板間で、光信号による情報伝達を行なう光学式プロセッサ間結合網において、前記各基板上の光デバイスは、同一の光通路上に配設されることを特徴とする光学式プロセッサ間結合網。

【請求項5】 面型光素子のアレイを具備し受光した情報をデバイスの裏面から出力可能な光デバイスを、基板 30 面に垂直な方向に光が通過できる基板領域に搭載し、第一の光デバイスの所定の位置の面型光素子から入力光ピームの位相、波長、強度の少くともいずれか1つを第一の光デバイスへの入力情報により制御されるバイアス印加により変調した光ピームをして出力し、第二の光デバイスの所定の位置にある受光素子で受光しつつ第三の光デバイスに向けて光ピームを出力するという様式の繰り返しで形成される光ピームの束を、第一の光デバイスに戻るように導くことにより光リングバスを形成し、この光リングバスを用いてプロセッサ間通信を実現すること 40 を特徴とする光学式プロセッサ間結合網。

【請求項6】 前記光デバイスは、第一の光デバイスからの光ビームを第三の光デバイスに通過させる第二の光デバイスの中継用素子と、第二の光デバイスへの入力情報に基づいて光ビームの位相、被長、強度の少なくともいずれか1つの変調する第二の光デバイスの送信用素子と、メッセージを第二の光デバイスに取り込む口となる受信用素子からなるセルのアレイを具備する請求項7記載の光学式プロセッサ間結合網。

【請求項7】 前記光デバイスは、第一の光デバイスか 50 により、光バスによる超並列コンピュータを構成するこ

らの光ピームを第三の光デバイスに通過させる第二の光 デバイスの中継用素子と、第二の光デバイスへの入力情 報に基づいて位相、波長、強度の少なくともいずれか1 つを変調する送信用素子を具備する請求項7記載の光学 式プロセッサ間結合網。

【発明の詳細な説明】

[0001]

【産業上の利用分野】本発明は、光素子及び超並列コンピュータにおける複数のマイクロプロセッサ間の通信に供される光バス、そして、これらの光素子、光バスを用いて構築される光学式プロセッサ間結合網に関する。

[0002]

【従来の技術】近年、半導体技術とアーキテクチャ等の 研究により、コンピュータの処理能力の向上が図られて いる。そして、盛んに研究されている処理能力向上の手 段の一つとして、複数のマイクロプロセッサを用いて並 行的に処理を進める方法がある。最近では、数千~数万 のマイクロプロセッサを並列に動作させる超並列コンピ ュータの実現が研究されている。しかし、多くのマイク ロプロセッサを並列動作させる場合、マイクロプロセッ サ間の通信路であるバスが問題となる。超並列コンピュ ータにおいてマイクロプロセッサは、その全てを1ボー ド上に配置することは物理的に困難であり、また配線上 も不利なため、複数のボード上に分散して実装される。 したがって異なるボード上のマイクロプロセッサ間にお いてもデータのやりとりがスムーズに行えるボード間の バスが重要となる。また、最近の高性能なマイクロプロ セッサは動作速度も速く出入力するデータも高速・大容 量のものとなっているため、高性能な超並列コンピュー タでは、バスも高速・大容量の通信が可能なものである ことが必要となる。そのため、たとえば図37に示すよ うなバスが使用されている。このバスは隣合うボード8 0,81上のマイクロプロセッサ82,83のデータ入 出力を導線84により配線したものである。しかしこの 場合、ボード間の配線が大量になる、高速データ通信が 困難、あるいは任意のマイクロプロセッサ間通信を行う ためには、多くのマイクロプロセッサの中継が必要とい う大きな欠点があった。

【0003】そして最近では電気的なバスの代わりに、ボード間配線の簡素化、高速通信可能という利点をもつ 光通信を用いた光バスが超並列コンピュータを構成する のに適している。

【0004】3枚以上のボードからなる超並列コンピュータに使用される光バスを実現するには、データの送信を行うマイクロプロセッサが実装されているボードからの光信号は他のボードにおいて中継される必要がある。このような用途には光透過素子あるいは受光素子と発光素子を組み合わせた光素子が必要となる。そして、光素子を面型にアレイ化したデバイスを各基板で用いることにより、光バスによる超並列コンピュータを構成することにより、光バスによる超並列コンピュータを構成するこ

30

とができる。また、このような基板間光接続方式は、超 並列コンピュータ以外にも大容量交換機のような大容量 の通信を多く扱うシステムに適用できるものである。

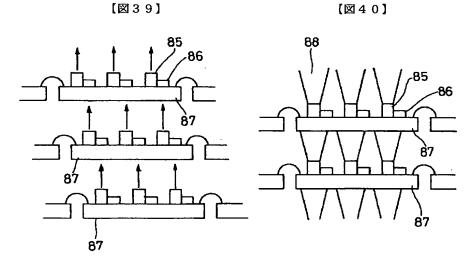

【0005】このような特徴をもつ光素子は、これを集 積化した面型光素子アレイの性能・実現性・使い易さを 左右する重要な要素となる。現在までに光透過素子とし ては面型半導体レーザ増幅器が、発光素子と受光素子を 同一半導体基板上に集積化したものとしては、図38に 示すような発光素子85と受光素子86とを横に並べた ような素子が研究されている。

【0006】図38の素子は、普通は素子上部からの光 信号を受光しかつ素子上部へ光信号を出射するが、使い 方により素子下部からの光信号の受光も可能なので前記 面型光素子アレイの構成素子として使える。しかし、こ の横並び構造の素子により前記面型光素子アレイを構成 すると、隣合うボードの発光部と受光部を対向させるた めに、図39に示すようにボード相互の位置をずらして 配置するか、図40のようにデバイス上の素子の密度を 減らし、かつ出射光88の放射角を広げることにより、 素子相互の結合を行うかしなければならないという問題 20 がある。さらに、重要な問題点として、入射する光信号 をそのまま出射光信号として透過させる光透過素子を用 いた場合に、透過光が次のボード上にある面状発光・受 光デバイス上の受光部に向かっていないため、複数ボー ド間での光バスの実現が困難である。

【0007】さらにアレイの入射側では隣の基板から発 射された光信号は回折によりビーム径が広がるため、受 光素子以外のところへも光信号が当たる。そして素子以 外の場所に当たった光信号は、たとえば反射して隣の基 板へ戻り、光透過素子や発光素子の特性を劣化させた り、あるいは、自基板内で光電子を励起し雑音として受 光素子出力や発光素子の変調等に影響を与えてしまう。 【0008】また、従来においては、複数の基板からな るシステムの実装にはバックプレイン(マザーボード) やケーブルが使用されていた。しかし超並列計算機のよ うに基板上に多数のプロセッサが搭載され、別の基板上 のプロセッサと多数の通信路を設ける必要がある場合 は、従来の方法では基板の一辺からバックプレインやケ ープルへ取り出せる信号線数に限界があるため、疎らな 結合トポロジーを用いたり、通信路のビット幅を落とす 40 などして配線数を減らすため、十分な通信性能を得られ ないことがあった。

【0009】また電気的配線を行う場合、超並列計算機 のような大規模なシステムにおける離れた基板との配線 では、基板内部に比較してタイミング的制約が厳しく、 ノイズの影響も受け易いので周波数を高速にすることは 困難であった。そのため配線本数を多くして通信性能を 確保する必要が生じたりするが、上記のようにあまり多 くの電気的配線をパックプレインに出すことは困難であ る。ケーブルを用いて接続する場合はラインドライバが 50

大量に必要になるなど高密度実装と消費エネルギーの観 点からも電気的配線には欠点がある。

【0010】一方、帯域が広いこと、浮遊容量による信 号のなまりや遅延が少なく高速であること、アース線が 不要なこと、ノイズを受けにくいことなど、光を通信に 用いる利点は大きい。

【0011】このため近年では光LANが実用化されて いる。またディジタル交換用計算機でファイバー束を用 いた基板間通信を行った例もあり、数本の光ファイバー 束を用いたディジタル光リンクは実用化されている。し かし、これらのように少ない本数の光信号で電気的なバ ックプレインを走る千本の中速電気信号の転送速度を飛 躍的に上回ることは困難である。また超高速化すること で少ない本数の光信号で非常に多くの電気信号をおきか えることができたとしても、信号の多重化と分配に対す るハードウェアコストがかかる。

【0012】並列計算機のプロセッサ間結合網を自由空 間を伝搬する光ピームを用いて構築した例もあるが、そ れらはホログラムを取り替えたり、手動で受信装置を動 かしたり、液晶スイッチを用いて構成を切り換えるので 回線接続に時間がかかるという欠点がある。

【0013】このほかに光導波路を形成したバックプレ インを用いる構想が報告されている。バックプレインを 用いる場合は最大構成時の大きさがバックプレインのサ イズで抑えられてしまうという欠点がある。

【0014】さらに、発光素子アレイチップと受光素子 アレイチップを向かい合わせてプロセッサ間結合網を自 由空間を伝搬する光ビームを用いて構成する構想も報告 されている。しかし、この場合二枚の基板間は直接通信 できてもより多くの基板との通信路を光で作ることは困 難である。

【0015】円筒形の鏡で自由空間を伝搬する広がりを 持った光ピームを反射させ放送バスを構築した例もある が、反射角は限られるので鏡を遠くに置かない限りあま り多くの基板間を接続できず、鏡から基板を離すにつれ て位置合わせが困難になってくるという欠点がある。ま たこの方式ではプロセッサからの出力光信号の論理和が 取られてしまうバス構成であり、クロスバ結合などに比 べるとはるかに能力が低い。

#### [0016]

【発明が解決しようとする課題】上述した如くの特徴を もつ光素子は、これを集積化した面型光素子アレイの性 能・実現性・使い易さを左右する重要な要素となり、現 在までに光透過素子としては面型半導体レーザ増幅器 が、発光素子と受光素子を同一半導体基板上に集積化し たものとしては、図38に示すような発光素子と受光素 子を横に並べたような素子が研究されている。

【0017】また最近研究されている面型半導体レーザ 増幅器は入射光を増幅して出射するため多段の基板によ る中継が行われても高品質な基板間通信が実現できる。

しかし、受光素子と発光素子を別途用意しなければならない点や、リング状の光バスを構成した際に発生する周回光を除去できない点が問題となる。

【0018】図38の素子は、普通は素子上部からの光 よって通信号を受光しかつ素子上部へ光信号を出射するが、使い 方により素子下部からの光信号の受光も可能なので前記 複数の光面型光素子アレイの構成素子として使える。しかし、こ の横並び構造の素子により前記面型光素子アレイを構成 すると、隣合うボードの発光部と受光部を対向させるた めに、図39に示すようにボード相互の位置をずらして 10 とする。配置するか、図40のようにデバイス上の素子の密度を 減らし、かつ出射光の放射角を広げることにより、素子 相互の結合を行うかしなければならないという問題点が 子を前記ある。

【0019】さらに、重要な問題点として、入射する光信号をそのまま出射光信号として透過させる光透過素子を用いた場合に、透過光が次のボード上にある面状発光・受光デバイス上の受光部に向かっていないため、複数ボード間での光バスの実現が困難である。さらに、アレイの入射側では、隣の基板から発射された光信号は、回20折によりビーム径が広がるため、受光素子以外のところへも光信号が当たる。そして、素子以外の場所に当たった光信号は、たとえば反射して隣裡の基板へ戻り、光透過素子や発光素子の特性を劣化させたり、あるいは、自基板内で光電子を励起し雑音として受光素子出力や発光素子の変調等に影響を与える。

【0020】また、超並列コンピュータを実現するには、そのマイクロプロセッサ間に発生する高速・大容量の通信を処理するバスが必要となる。しかし、従来の手法では煩雑な配線や高速通信への限界、フレキシブルな 30プロセッサ間の通信が困難といった問題点があった。

【0021】一方、従来におけるプロセッサ間結合網においては、電気信号による基板間配線であるため、ノイズによる信頼性の低さや、周波数的にも高速化が困難という欠点がある。

【0022】この発明はこのような従来の課題を解決するためになされたもので、その第1の目的は、信号伝達を円滑に実施し得る光素子、及び光バスを提供することである。また、第2の目的は、電気式に比べ基板間転送周波数を高速化し、ノイズによる信頼性低下を抑制し、基板間配線本数を飛躍的に増加させ、さらに、少ないハードウェア量を用いて接続可能基板数を多くしたうえで、クロスバ網に近い密なトポロジーを持つ超並列計算機むけ結合網を高密度に構成するとともに、従来の手動式や液晶式などに比べて高速な接続の切り換えを可能にし得る光学式プロセッサ間結合網を提供することである。

#### [0023]

【課題を解決するための手段】上述した目的を達成する ために、本願第1の発明は、基板と、この基板に設けら 50

れた発光素子と、前記基板の発光素子の周囲に設けられた同心円状の発光素子とを具備したことを特徴とする。 【0024】第2の発明は、複数のボード間を光信号によって通信するための光バスであって、前記複数のボードにマトリックス状に配置され、光信号の送受信を行う複数の光素子と、他のボードから送信された光信号を前記光素子を介して受信した自己のボードに取り込む受信部と、自己のボードで発生した信号を前記光素子を介し

【0025】第3の発明は、前記光素子は受光素子と発光素子とを具備し、前記マトリクス状各行の前記受光素子を前記ボード上の複数のマイクロプロセッサの入力端子に対応付けて接続し、前記マトリクス状各列の前記発光素子を前記マイクロプロセッサの出力端子に対応付けて接続し、前記各ボード上の複数のプロセッサ間で通信するようにしたことを特徴とする。

て他のポードへ送信する送信部とを具備することを特徴

【0026】第4の発明の光学式プロセッサ間結合網は、表面で受光した光信号を裏面から出力可能な光デバイスを有する複数の基板間で、光信号による情報伝達を行なう光学式プロセッサ間結合網において、前記各基板上の光デバイスは、同一の光通路上に配設されることを特徴とする。

【0027】第5の発明の光学式プロセッサ間結合網は、面型光素子のアレイを具備し受光した情報をデバイスの裏面から出力可能な光デバイスを、基板面に垂直な方向に光が通過できる基板領域に搭載し、第一の光デバイスへの入力情報に基づいてバイアス印加により所定の位置の面型光素子から入力光ビームの位相、波長、強度の少なくともいずれか1つをバイアス印加により変調した光ビームとして第二の光デバイスの所定の位置にある受光素子で受光しつつ第三の光デバイスに向けて光ビームを出力するという様式の繰り返しで形成される光ビームの束を、第一の光デバイスに戻るように導くことによりリングバスを形成することを特徴とする。

【0028】第6の発明の光デバイスは、面型光素子のアレイを具備し受光した情報をデバイスの裏面から出力可能な光デバイスにおいて、第一の光デバイスからの光ピームを第三の光デバイスに通過させる機能を有する中継用第二の光デバイス素子と、第二の光デバイスへの入力データ情報に基づいて光ピームの位相、波長、強度の少なくともいずれか1つを変調する送信用素子と、メッセージを第二の光デバイスに取り込む口となる受信用素子からなるセルのアレイを具備させることを特徴とする。

【0029】第7の発明の光デバイスは、面型光素子のアレイを具備し受光した情報をデバイスの裏面から出力可能な光デバイスにおいて、第一の光デバイスからの光ピームを第三の光デバイスに通過させる機能を有する第二のデバイスの素子と、第二の光デバイスの素子と、第

二の光デバイスへの入力情報に基づいてバイアスを印加 して位相、波長、強度の少なくとも1つを変調する素子 を兼用にすることを特徴とする。

7

[0030]

【作用】本発明による光素子は、受光素子を光透過素子 または発光素子の周囲に同心円状に形成することによ り、出射光を入射光が受光するのと同じ場所から発射さ せるため、入射する光と出射する光の光軸が一致する。 したがって、本発明による素子により構成した面型光素 子アレイを用いて基板間用光バスを構成すると、基板間 10 の発光部と受光部を対向させる機構を全ての基板間にお いて同一に設計できる。しかも、光透過素子または発光 素子を受光素子の内側に配置することにより、受光部の 直径は従来と変わらず実際に受光する部分の面積の減少 もまた最小に抑えることができるため、受光効率もあま り劣化しない。具体的には素子中心部の光透過素子また は発光素子には、半導体基板の面と垂直な方向に光を発 射でき、集積化、アレイ化が可能で、光通信に適した光 を出射する素子である面型半導体レーザ増幅器または面 型半導体レーザ発振器を利用することが考えられる。こ 20 の場合の透過・発光部は、標準的には5~10μm、最 大でも直径20μm程度にしかならず、逆に受光部外径 は50~100µm程度であり、回折の影響を考えると 入射する光信号のピーム径は100μm以上に広がって いるため、面積比で考えて中心部の影響はほとんど問題 にならない。

【0031】また、光透過素子を用いた場合、透過光は 次のボード上にある面型光素子アレイ上の受光部に向か って進むことになるため、容易に透過機能を利用しての となる。これは、受光素子と発光素子の組み合わせを用 いた場合には、入射する光信号を必ず一度電気信号に変 換してからでないと次ポードに中継できなかったことと 比較すると、光バスの処理能力向上、面型光素子アレイ の消費電力低下という大きな利点がある。

【0032】前述のように透過・発光素子として面型半 導体レーザ素子を用いる場合、その活性層を量子井戸構 造とすることにより、増幅・発光の効率を向上させ、消 費電力を低下させることができる。また、光透過素子と して用いている場合には、量子井戸構造の優れた透過率 40 変化特性により光の透過/遮断を制御できる。前記光の 透過/遮断の機能は、光バスをリング状に構成した際に 生じる間隔で、一度バスに注入された光信号がいつまで も周回してしまう、いわゆる周回光の発生を防ぐことが できる。光の透過を妨げる機能は、量子井戸構造以外に も、素子中に屈折率を制御できる物質を多層に成長させ た格子の層をつくりこんでおく等の手段により具備させ ることができる。

【0033】また、光透過素子として面型半導体レーザ 増幅器を用いた場合、活性層の両側に屈折率を制御する 50

ことのできる層を設けることにより活性層両側の反射率 を高くすることができる。この状態で活性層に電流を注 入することにより、このレーザ素子はレーザ発振を起こ すため、特に発光素子を別に設ける必要がなくなる。

【0034】さらに、前記アレイの入射側では、隣の基 板から発射された光信号は回折によりピーム径が広がる ため、受光素子以外のところへも光信号が当たる。そこ で、素子以外の部分に無反射膜をコーティングしたり、 または光吸収層をつくりこんでおくことにより、前記の ような素子以外の場所に当った光信号が、たとえば反射 して隣の基板へ戻り光透過素子や発光素子の特性を劣化 させたり、あるいは自基板内で光素子を励起し雑音とし て受光素子出力や発光素子の変調等に影響を与えること が防げる。

【0035】本発明の光バスの作用を以下に説明する。 【0036】この面型光バスは、バス信号として光信号 を用いる。このため光ビームの集束性の良さを用いるこ とにより、ボード間を空間伝搬した後にも、たとえば1 0 0 μm以下の間隔で並ぶ受光素子の一つだけに信号を 伝えることが可能となる。したがって、ボード間の配線 が不要となり、配線労力の省力化や保守性の向上につな がる。また電気配線は配線間容量等により帯域制限が生 じ易く、また配線間の漏話もあるが、光配線を用いると これらの制限は生じないため、高速で高性能な通信が容 易に実現できる。

【0037】また、片面に発光素子をもう一方の面に受 光素子をマトリックス状に集めた面状発光/受光デバイ スを用いることにより、ボード間通信のために多く必要 となる発光/受光素子の実装/配線の簡略化や容易なデ 複数のボード間での光信号の送受を実現することが可能 30 バイス製作が可能で、配線数の増大が全く問題にならな い。そしてボード間の配線を増やすことにより、このシ ステムでの通信方式・手順のフレキシビリティが向上さ せることができる。さらに、光増幅器や光再生中継器の 技術を受光素子と発光素子の間に用いて受信信号の中継 機能も設けることにより、隣合わないボード上のマイク ロプロセッサ間の通信をより少ない遅延時間で実現でき

> 【0038】本発明の光バスは、前記請求項2中にある ような面状発光/受光デバイス上の発光素子の各列をボ ード上の各マイクロプロセッサに対応させると同時に、 受光素子の各行も各マイクロプロセッサに対応させる配 線を行うことにより、ボード間の任意のマイクロプロセ ッサ同士の通信を容易に実現させることが可能となる。 【0039】本発明の光学式プロセッサ間結合網の作用 を以下に説明する。

【0040】第5の発明の光学式プロセッサ間結合網が 面型発光素子のアレイを具備し受光した情報をデバイス の裏面からの出力可能な光デパイスを、基板面に垂直な 方向に光が通過できる基板領域に搭載するので、第一の 基板上の光デバイスから出力した光を、対面する第二の

10

基板上の光デバイスに導くことができる。本発明の実施例としてGaInAsP/InAsP、GaInAs/InAlAs、GaAlAsSb/GaAsSbの超格子積層膜構造を構成するAPD(なだれ増倍型受光素子又はGaAlAs/GaAsを面型発光レーザ素子としての活用が各々の光デバイスは入力データ情報、メッセージ、命令に基づいたバイアス印加により入力光ビームの位相、波長、強度の少くともいずれか1つを変調した光ビームを出力できるので、どのデバイスでも送信元とすることができる。第一のデバイスを送信元とすると、第二の光デバイスは受光した情報をデバイスの裏面から出力可能なので、第二の基板に対面する第三の基板上の光デバイスに第一のデバイスからの情報は伝達される。

【0041】光素子はアレイ状になっているのでこのような光ビームが束状になって基板を貫くことになる。このようにして作られる光ビームの束を第一の光デバイスに戻るように導くことによりリングバスを形成しているので、次々と光ビームが伝搬していくとやがて任意の送信先の基板に光ビームは到達することができる。

【0042】各々のデバイスは対面する基板上の光デバ 20 イスに向けて光ビームを出力しつつ受光素子で受光することにより第一のデバイスからの情報を取り込むことができる。このようにして第7の発明によれば任意の基板間の通信が可能な光による高速でノイズに強いバスを多数本設置することが可能となる。

【0043】第6の発明の光デバイスは、面型受光素子のアレイを具備した光デバイスにおいて、第一の光デバイスからの光ピームを第三の光デバイスに通過させる第二の光デバイスへの入力メッセージを実行する機能を有する中継用第二の光デバイスの素子を具備するので光ピるしたができる。また各々の光デバイスは第二の光デバイスからの光ピームの位相、波長、強度の少なくともいずれか1つを変調する素子を具備するので、デバイスに入力された情報を送信することができる。また各々の光デバイスはメッセージを第二の光デバイスに取り込む口となる素子を具備するので、光ピーム上に出力されている情報を受信することができる。

【0044】以上の2つの機能を備えたセルをアレイ状 40 にしたデバイスを実現することにより、光により情報を送信したり、受光した情報を取り込んだり、デバイスの裏面から出力することが可能なセルのアレイができる。このようなデバイスを用いることにより第一の発明を実施する手段が与えられる。

【0045】第7の発明の光デバイスは、面型光素子のアレイを具備し受光した情報をデバイスの裏面から出力可能な光デバイスにおいて、第一の光デバイスからの光ピームを第三の光デバイスに通過させる第一の光デバイスからの入力メッセージを実行する機能を有する中継用 50

第二の光デバイスの素子と、その中継用第二の光デバイスへの入力データ情報に基づいてバイアスを印加し第一の光デバイスからの光ピームを位相、波長、強度の少くてもいずれか1つを変調する素子が兼用になっているので、セルの面積が節約できるることを特徴とし情報を送信しているセルは光リングへの送信の競合がない場合は、送信の機能と中継の機能を同時に使用することはないので兼用になっていても問題はない。

[0046]

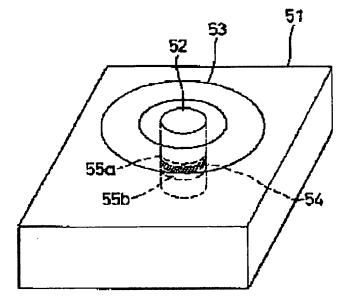

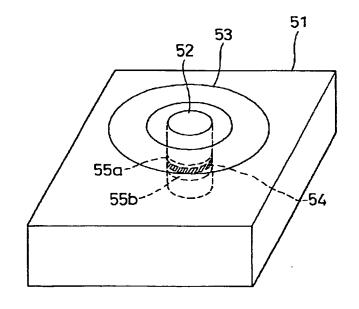

【実施例】以下に図を用いて本発明の実施例を説明する。図1は本発明に係わる一実施例の光素子の構成を示す図である。

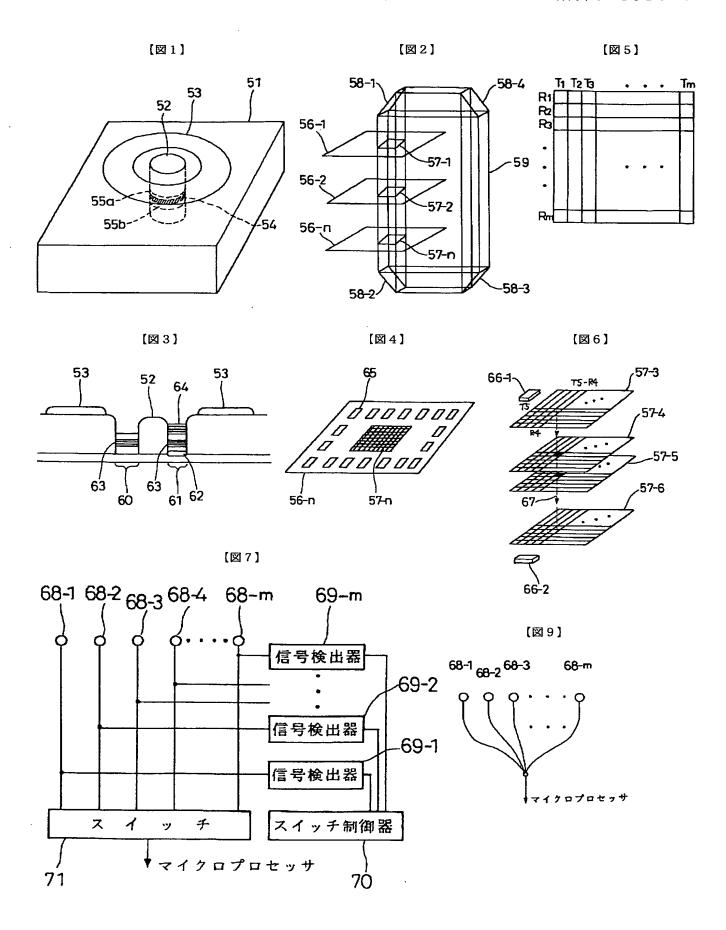

【0047】本実施例の素子は半導体基板51の中央部 に発光・透過機能をもつ発光・透過素子52があり、そ の周囲を受光機能をもつ受光素子53が取り囲む配置と なっている。そして、受光素子53は下面からの入射光 を電気信号に変換する。そして出射光は発光・透過素子 52の上面から発射される。中央部は多層構造で、その 中には活性層54を有している。活性層54に電流を注 入することによりレーザ光を発光したり、透過光を増幅 する。発光機能と透過機能とは活性層54の上下にある 層55a, 55bを制御して行う。たとえば電流により 活性層54の上下にある層55a,55bの屈折率を制 御して活性層54両端の反射率を変化させる。反射率が 高いときには、中央部は面発光半導体レーザと同じ原理 によりレーザ発振が生じるとともに入射光は発光・透過 素子52を透過できなくなるが、逆に反射率が低いとき には中央部はレーザ増幅器として動作し、入射光は増幅 されながら透過するがレーザ光の発振は生じない。さら に、活性層54に量子井戸構造を用いることにより、透 過機能の高速なon/off、発光機能・増幅機能の低 消費電力化が実現できる。本実施例の素子においては活 性層54の大きさが一般の半導体レーザの活性層54よ り小さいため、量子井戸構造による効果は一般のレーザ において得られる効果より大きく、高性能な素子が実現。 できる。また図2に示すようなリング状の光バスを構成 した場合に問題となる周回光に対しては、特に透過機能 のon/offを行うスイッチとしての性質が、周回光 の消滅を容易にする。なお、56-1~56-nはマイ クロプロセッサボード、57-1~57-nは面状発光 ・受光デバイス、58-1~58-4は反射鏡、59は 光信号光路を、それぞれ示している。

【0048】周囲に同心円状に構成された受光素子53 も多層構造から構成される。ただし層構造は中央部とは 異なり、フォトダイオードの構造にして受光素子53を 実現する。裏面入射であるから受光部分の最上層には電 極を設けることができ、反射・散乱等による上面からの 不要光による雑音を防ぐことができる。また、受光部分 は環状であるため表面積は若干狭くなるが、受光範囲は 100μm四方~と広く、逆に直径が数~十数μm程度 な中央部の出射口からは回折により放射角の広い光が発 射されるため、一般的なボード間隔(2~3 c m程度) の光送受では、位置調整は比較的容易である。もしも、 放射角と基板間距離の関係から光ビームが広がり過ぎて 隣の光素子でも受光できるような場合には、出射口にレ ンズを設けてビームを絞るとか基板間に導波機構を設け る等の対策が必要となる。この際のレンズも半導体材料 により素子の一部として設ける方法やマイクロレンズア レイ板を用いる方法がある。

11

子の構成を示す図である。

【0050】同図において、60は面型半導体レーザ増 幅器、61は面型半導体レーザ発振器、62は反射層、 63は活性層、64は反射格子層を示している。図1に 示す実施例のような発光機能と透過・増幅機能を同一の 活性層で実現し、また、そのために両機能を切り替える 機能を設けることは、高性能な光素子の製作を困難にす るので、発光機能の部分と透過・増幅機能の部分を並列 して持った素子となっている。これにより発光機能の部 分では活性層63の上下の層を反射専用の層として安定 20 して生成できるし、また、この層を制御するための機構 も不要となる。逆に透過部分は量子井戸構造により光ス イッチ機能も併せ持たせて、希望しないときには光を透 過させなかったり、発光しながら入射光も透過させる機 能を実現できる。

【0051】つぎに図2に示す光バスを用いたm×nプ ロセッサ超並列コンピュータについて説明する。

【0052】この光バスはm個のマイクロプロセッサを 各々に実装したn枚のポード56-1~56-nが縦に 並べて配置されている。各ボードには面状発光/受光デ 30 バイス57-1~57-nがある。このデバイス上に は、図4に示されているように発光/受光素子がm×m マトリックス状に並んでいる。このようにポード間通信 に必要な光素子を一ケ所に集中させることにより、素子 を集積化したデバイスを実現することが可能となり、実 装や配線が容易になる。面状発光/受光デバイスは、ボ ード上の任意の位置に配置可能だが、マイクロプロセッ サとの配線、デバイスからの端子の出し方等を考えると 図のようにポードの中央部に配置するのが適している。 全ての発光/受光素子はポード上のm個のマイクロプロ 40 セッサ65のいずれかと接続されている。ボード間の通 信は光空間伝搬で行う。ボード56-1の下面から出射 された光信号は、ボード56-2の上面で各々受信さ れ、あるいはポード56-2で発生する信号光と合成さ れ、ボード56-1の下面からボード56-3へ向けて 出射される。この繰り返しにより信号光は逐次伝搬さ れ、最後のポード56-nから出射された光信号は、反 射鏡58-2,58-3,58-4,58-1により反 射されてボード56-1の上面より入射されるようにす る。これにより各発光/受光素子間の信号光の束は図2 50 データ送信後一定時間内に受信側からの返事がない場合

に示されるような軌跡59を描き、各マイクロプロセッ サ間の通信が実現できる。

【0053】異なるボード上にある任意のマイクプロセ ッサ間の通信方法は次の通りである。

【0054】今、ポード56-3のマイクロプロセッサ No. 5 (以下、プロセッサ[3,5]と呼ぶ) からボ ード56-6のマイクロプロセッサNo. 4 (同様に以 下、プロセッサ [6, 4]) へのデータ伝送を例にと る。各マイクロプロセッサは面状発光/受光デバイスの 【0049】また、図3は本発明の第2の実施例の光素 10 ある特定の列の発光素子とある特定の行の受光素子とを 制御できるように配線されている。たとえば、図5はポ ード56-3上の面状発光/受光デバイス57-6を示 している。

> 【0055】プロセッサ[3,5]は面状発光/受光デ バイス57-6の列T5上の任意の素子を用いて送信が 可能であり、また行R5の受光素子に達した光信号を受 信できる。プロセッサ[6, 4]も同様にボード56-6上の面状発光/受光デバイスのT4とR4に接続され ている。プロセッサ[3,5]は、プロセッサ[6,

> 4] へ伝送するデータを受信者情報等を付加した伝送用 データへの変換処理をしたのちに、列T5、行R4の位 置にある発光素子を用いて面状光バス上へ送出する。こ の様子を簡単に図示したのが図6である。同図において 66-1は、送信側プロセッサ[3,5]を66-2は プロセッサ [6, 4] を示しており、また点線67はポ ード間を伝送される信号光を示す。送出された信号光は ボード56-4, 56-5の面状発光/受光デバイスの T5-R4の位置にある素子により中継され、ボード5 6-6の面状発光/受光デバイスのT5-R4にある受 光素子により受信され、プロセッサ [6, 4] にデータ が届く。プロセッサ [6, 4] からは、データ伝送が成 功したことを示すACK信号が、今度はT4-R5の位 置の発光/受光素子を用いて同様にしてプロセッサ

> [3, 5]に伝送され、一連のデータ伝送は終了する。 【0056】このデータ伝送において、ボード56-4,56-5におけるデータの中継は、信号光を一度受 信し、そのデータ中の情報から自ボード宛の信号かどう かを判断し、他ボード宛の信号の場合は中継を行うよう にする。

【0057】また、信号が確実に伝わるようにするため に、信号衝突に対して2つのレベルでの取り決めが予め 必要となる。まず送信側の段階であるが、前記の方法で は任意のボードのマイクロプロセッサNo. 5が任意の ボードのマイクロプロセッサNo. 4にデータ伝送する 際は、各ポードの同じT5-R4の位置にある発光/受 光素子から光路が形成され信号光を伝送することにな る。このような伝送が複数同時に生起した場合には複数 の信号光が重なるため、各受信端末は受信不能となる。 この状況に対処するために、送信側はタイマを用意し、

は、信号の衝突が発生したと判断して再送を行う。また、送信側は送信前に該当する光路をチェックして他の信号光が存在しないことを確認することにより、より信号衝突の確率を下げることができる。

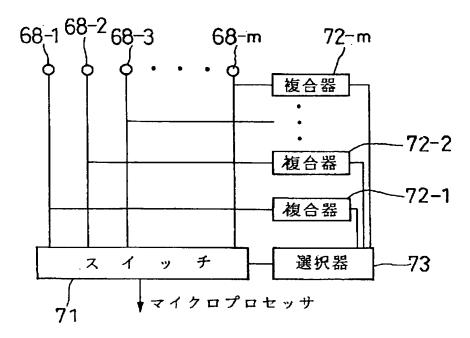

【0058】次に受信側を考えると、同じ受光素子に複 数の信号光が達する場合の対応は前記の送信側での制御 により問題とならないが、接続されている行上の異なる 受光素子に同時に入ってきた自ボード宛の信号光の処理 が必要である。このために、図7に示すような受光素子 68-1~m個々に信号検出器69-1~mを備え、こ 10 れら検出器の全出力はスイッチ制御器70に接続され、 スイッチ制御器70では早い者勝ち制御により最初に信 号が検出された受光素子からのデータだけをマイクロプ ロセッサに接続するようにスイッチ71を切り替える。 この場合に選択されなかった信号は廃棄されるが、送信 側は前記のタイマにより適宜再送を試みることにより後 で送信が行われる。また受信側での制御として早い者勝 ち制御以外に、図8に示すような各受光素子に復号器7 2-1~mを設け、同時受信が生じた場合には選択器7 3において送信者や通信内容によりマイクロプロセッサ 20 に接続する信号を決定する制御や、図9のように全受光 素子68-1~mをそのまま合成してマイクロプロセッ サに接続し、同時受信により復号できなかった場合は前 記送信側のタイマによる再送を持つ制御も考えられる が、前者は処理が複雑であり、後者は通信路の利用率が 悪いことを考えると図7の方式が適していると考えられ る。

【0059】以上の説明では、他のボード上のマイクロプロセッサ間通信を仮定したが、同じボード上のマイクロプロセッサ間の通信においても前記と同様の方法で本 30発明の面状の光バスを用いることが可能である。この場合、光バスの伝送情報量の増大、不要な遅延時間の増加という問題が生じるが、ボード上の配線、スイッチング要素を減少できる利点もある。

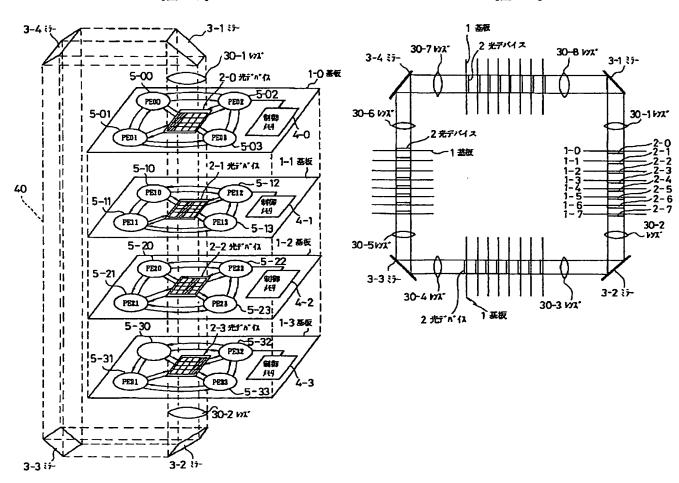

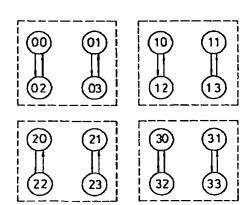

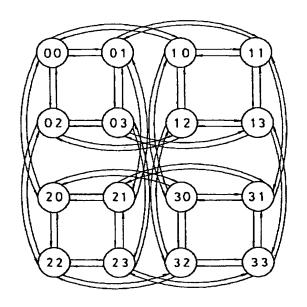

【0060】図10は本発明を適用した並列光リングバスを具備する並列計算機における光学式プロセッサ間結合網の第3実施例の構成を示す模式図である。本実施例においては、4個のプロセシングエレメントを具備する基板4枚から形成されている。

【0061】PE00 5-00、PE01 5-0

PE02 5-02、PE03 5-03は基板1-0

上の0番から3番のプロセシングエレメント、PE10 5-10、PE11 5-11 PE12 5-1

2、PE13 5-13は基板1-1上の0番から3番のプロセシングエレメント、PE20 5-20、PE21 5-21、PE22 5-22、PE23 5-23は基板1-2上の0番から3番のプロセシングエレメント、PE30 5-30、PE31 5-31、PE32 5-32 PE33 5-33は基板1-3上

の0番から3番のプロセシングエレメントと名付けるこ 50

とにする。ここでは基板の番号に対応する座標をY座標、基板内部の位置に対応する座標をX座標と呼ぶことにする。

【0062】同一基板上の各プロセシングエレメントは 基板の配線パターンにより互いに結合されている。この 結合網はX座標の異なるプロセシングエレメントへの通 信手段を与える。本実施例においては、基板内をリング 結合したものを示しているが、基板内の結合形態は他の トポロジーであっても良い。なお、基板内部は多層配線 基板を用いることにより多くの配線を用いることで高速 な結合網を構築することができる。

【0063】別の基板上のプロセシングエレメントとの通信は基板に1個ずつ配置された光デバイスを介して行われる。そこで各プロセシングエレメントは光デバイスと通信するためのボートを備える。基板上の全プロセシングエレメントが光デバイスと結合されることになる。基板上には更に光デバイス制御用の制御メモリが搭載され、ここから読み出される情報は光デバイスに導かれる。制御メモリの読み出し書き込みは本実施例においては各基板の2番のプロセシングエレメントPE02, PE12, PE22, PE32が行うものとするが、全ての制御メモリからの読み出しを一斉に同期をとって行うことができれば何が行っても構わない。

【0064】以上のような基板を隣接する基板間の光デバイスの位置が一致するように固定し、基板1-0上の光デバイス2-0から出力された光が基板1-1上の光デバイス2-1に当たり、基板1-1上の光デバイス2-1から出力された光が基板1-2上の光デバイス2-2に当たり、基板1-2上の光デバイス2-2から出力された光が基板1-3の光デバイス2-3 に当たるようにする。基板1-3上の光デバイス2-3 から出力された光はレンズとミラーを介して基板1-0上の光デバイス2-0 に当たるように導かれる。

【0065】本実施例においては基板は4枚だけなのでシステムの大きさは小さいのでミラーやレンズの位置合わせは問題ないが、基板枚数が極端に多くミラー間の距離が極端に離れ位置合わせや支持が困難になった場合でも、本実施例の光ファイバーアレイを用いれば最下位の基板と最上位の基板を確実に接続することができる。まないたシンズ30の枚数が増加するが図11のように4箇所のミラー3とミラー3の間に基板1を多数配置して長距離の光路を回避しても良い。

【0066】図12は本発明の第4実施例に係わる光デバイスの構成を示した図である。本実施例の光デバイスは4つの入力ポート(10-0,10-1,10-2,10-3)と4つの出力ポートを持ち(12-0,12-1,12-2,12-3)、4つの光素子群セル9が導波路型合波器7と電気回路プロック6に接続されたプロックを4個備えている。

【0067】本実施例においては、電気回路ブロックが

導波路部と同じセルに接続されるので、ブロック毎に別のチップになっていても良いし、4つのブロック全てが 1つのチップに搭載されていてもよい。

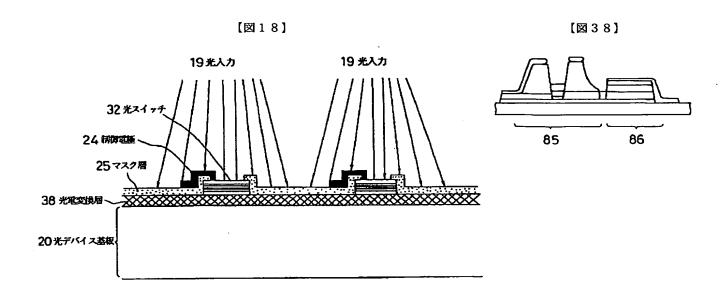

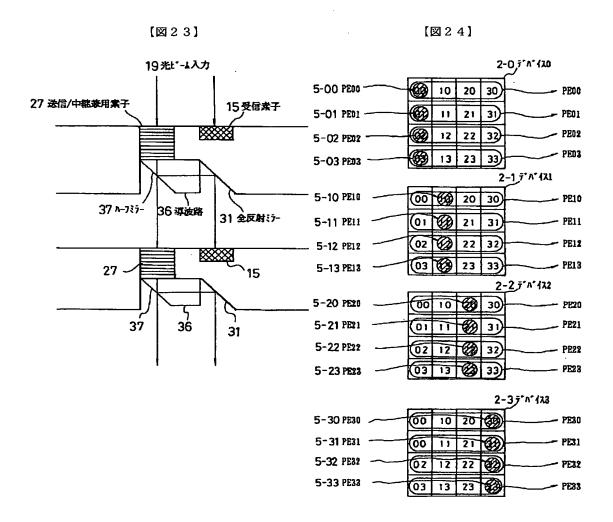

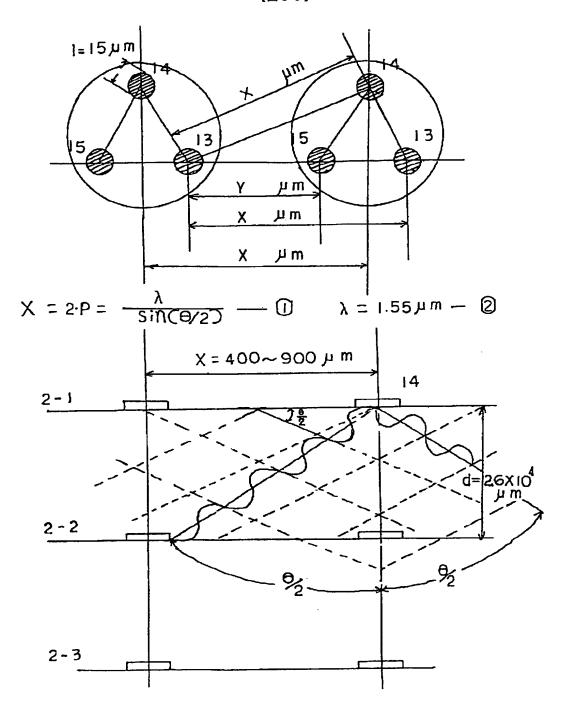

【0068】図13は本発明の第5実施例に係わる光素子群セル9の構成を示す図である。各セル9は受信素子15と中継素子14と送信素子13を具備する。受信素子15や中継素子14には光を通過させたり、阻止したまするスイッチング機能が必要になるが、Multiple Quantum Well (MQW)などを使えばデバイス面に垂直方向に入射される光をスイッチング 10する素子のアレイを構成できる。

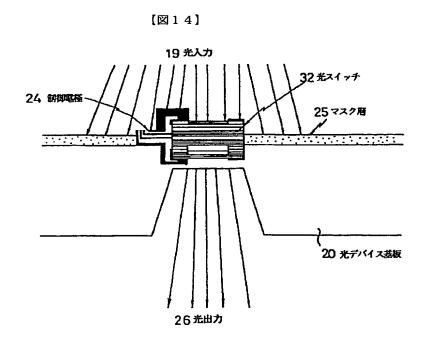

【0069】図14は中継素子14の断面図を示す。中継素子14は制御電極24によって通過状態と阻止・消光状態の2状態に制御され中継動作を行ったり、上からの光入力を消光・阻止する消光光スイッチ32からなる。例えばGaAlAs/GaAs面型発光レーザ素子やInGaAs/InAlAs系、ADP格子積層膜構造素子に入力された制御情報に基づいてバイアス電圧を印加して増幅作用光通過並びに、消光・阻止作用を行うものである。

【0070】図15は図13のA-B線に沿った受信素子15の断面図を示す。光デバイス基板20に形成された受信データ導波路16の上で面型の光スイッチ32を形成する。上から入射する光はこのスイッチ32の場所のみからしか受信データ導波路16側に通過できないよう他の部分はマスク層25でマスクする。この光スイッチ32は中継素子14と同様、制御電極24によって通過状態と消光・阻止状態の2状態に制御され、通過状態では上からの光は受信データ導波路16に通過する。図15においても前記面型発光レーザ素子、APD(なだ 30れ増倍受光素子)を用いてこれを可能にした。

【0071】図16は送信素子13の断面図を示す送信素子13としては面発光型の発光ダイオード(LED)、面発光型のレーザーダイオード(LD)や、増倍型発光素子(APD)などを用いれば電気信号により強度変調される送信素子13のアレイを構成することができる。電気回路プロックは基板番号に対応する制御入力10に基づいてセルを選択し、データ入力11によって送信素子13を変調する。プロセッシングエレメント自身のメッセージで変調させた増幅光を送信して周回して40戻ってきたデータを再びループに戻さないようにするために、送信が選択されたセルの中継素子14の中継動作を停止させるように制御する。

【0072】中継素子14と受信素子15は同時に同じ 光を受光し、中継素子14はそのセルが送信状態に選択 されていない場合に限り、受光した光を次の基板上の光 セルに送る。基板枚数が多い場合は第11の発明の光デ バイスを適用した本実施例の中継素子14に光増幅作用 を具備させ、広がりによる光強度減衰分を補う。

【0073】電気回路プロックは制御入力10の情報に 50 は2・P=λ/sin (θ/2)、2・P=X=400

基づいて導波路型合波器7に光を導くセルを選択し、受信素子15はそのセルが受信状態に選択されている場合に限り、受信した光を受信データ導波路16に通過させる。図12に示されるとおり一本の導波路型合波器7には複数のセルが接続され、その内の1つのセルが受信選択されるので受信選択された光のみが光電変換部に導かれる。光電変換部8に至るまでの損失と選択されていないセルから漏れ出る光の和によるノイズにより、選択された光の強度振幅が少なすぎると正しくデータを受信できなくなる。この場合は受信素子15に光増幅作用を具備させることにより改善することができる。

16

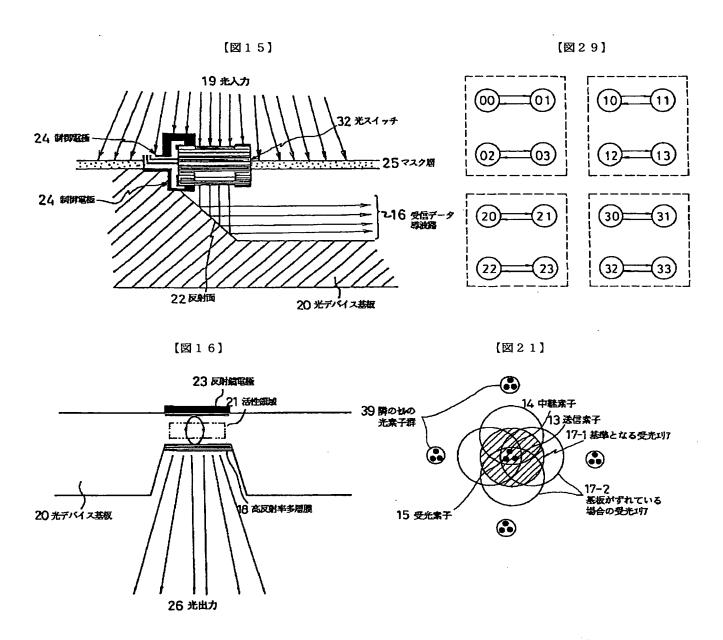

【0074】本実施例では受信した光情報を光のまま1本に集約しているが、図17のように受信素子15の下をくぐり抜けるように帯状の光電変換素子28を配置し、光電変換と集約操作をひとまとめにすることもできる。図18に帯状光電交換素子28を用いた受信部を図17の線C-Dによる断面図を示す。

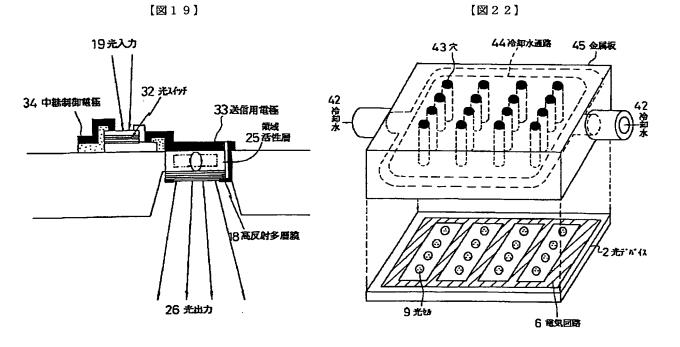

【0075】図17は本発明の第6実施例を示す構成図 である。同図に示されているように送信素子と中継素子 を兼用素子27にして光素子の種類を減らしてもよい。 図19は送信と中継を兼用とする素子の断面図を示す。 発光部の制御を光スイッチ32を介した入力光19と、 データ入力素子からの入力データを導く電気回路プロッ クの両方から行なえるようにすれば良い。送信する時は 電気回路プロックからの制御で発光させ、中継する時は 入力光による制御で発光させる。このようにすれば中継 動作時も能動的に発光するので段数を重ねても中継によ る光の減衰の問題は解決される。特に図14,図15及 び詳細には図35に示したGaAlAs/GaAs面発 光レーザ、InGaAsP/InAlAsP、InGa As/InAsP系超格子積層活性層構造を有する光増 倍型受光素子(APD)素子を用いて位相、波長、強度 の少なくともいずれか1つを制御し変調発光できること によりこの問題を解決した。

【0076】図20は複数のデバイス間の光のやりとりの形態を示す。この図は積み重なった光デバイス2を横から見たところである。送信素子13と中継素子14は下位に位置する光デバイスに向かって光を送信する。光は回折などによりある範囲に広がる。中継素子14による光が下位の光デバイス2-3を照らす範囲と送信素子13による光が下位の光デバイスを照らす範囲の重なりが受光エリア17である。真上に位置する光素子群セルからの光は円形の受光エリア17に広がり、隣の受光エリア17とは重ならないようになっている。これら3つの素子群の面積が受光エリア17に比べ十分小さければ図21に示すように基板間の多少のズレは許容される。又、図36で示すように発光素子の開口部直径Eを15μmとすると波長入が1.55μmの光ビームで入力しても図20、図21に示された入力光ビームの配光範囲

$\sim 900 \mu m$ , 0.  $099 \le \theta / 2 \le 0$ . 222 CX = $d \cdot t a n \theta / 2$ , d = 2.  $6 \times 10^4 \mu m$ , X = 40 $0 \sim 900 \mu m \sigma V - c d \cdot 44.8 \mu m < d \cdot t a$  $n \theta / 2 \le 100 \mu m c b X = 400 \sim 900 \mu m c$ 十分まにあう。又、ポート間隙距離がd=2.6×10 「の1/9でも十分設計できる。以上から受光エリア1 7の調節には中継素子14や送信素子13の開口部の大 きさと光の波長とデバイスの間隔を制御するのが簡便で あるが、他に図22に示すような穴の開いた板45を光 デバイス2に密着させても良い。この板45は光セル9 10 の位置に対応する位置に穴43が当てており、穴43の 内壁は反射率が高くなるように仕上げる。こうして光が 広がろうとしても穴43の中に閉じこめられる。板は金 属やセラミックのように光を通さず熱電導率の高い材質 で作り、冷却液42を通過させる通路を形成すれば効率 的な冷却をも可能にする。

17

【0077】この方法は穴43を開ける精度の問題から あまり光セル9の間隔を狭めることはできないが、光セ ル9の密度を高めたい場合は第20の発明の光デバイス を適用し、光セル9の位置に対応してマイクロレンズを 20 具備させることによっても受光エリア7の調節をするこ とが可能である。また発熱が少ない場合は多数の光ファ イバーを光セルの位置に合わせて並べ樹脂などにより一 体成形した光ファイバーアレイを光デバイスに密着させ ても受光エリアの調節をすることが可能である。

【0078】光素子が極めて高集積化されて光ピームの 指向性が鋭く、光セルの間隔が狭い場合は図23に示す ように第14の発明を適用し、ハーフミラー37などに より光を分岐させ受信素子15と送信、中継兼用素子2 7に導いても良い。

【0079】以上では全ての光デバイスの同一番号のセ ル間のみを光で結合する場合に付いて述べたが、上記の 光デバイス2間に導波路36を具備した板を配置するこ とにより、必ずしも番号が一致しないセル間を光で結合 することができる。

【0080】図24は各プロセシングエレメント5に対 応する受信セルの位置の設定例を示す図である。この例 では送信プロセシングエレメント5を一本の光ビームに 割り当てた場合を示す4×4のます目を各光デバイス2 におけるセルに対応し、数字はセルの番号に適応する。 斜線を配した番号のセルの送信素子はセル番号と同じ番 号を持つ同一基板上のプロセシングエレメントの出力デ ータにより変調されて発光する。

【0081】図23において各デバイスの長円で囲まれ たセルに受信された光のうち1本が選択されて長円中に ある送信セルと同一の番号のプロセシングエレメントに 導かれる。

【0082】送信セルの番号はプロセシングエレメント と対応するので、4つのデバイス上の同一番号のセルは その内の一つだけから発光される光ピームの情報を共有 50 ス)に注目して制御メモリ4-0の内容を决定する。

することになる。すなわち一本の光ピームに対応するバ スに送信するセルは1つであり光ビームに対する基板間 の競合はなく、受信することのできるプロセシングエレ メント5である。またX座標が等しい4つのプロセシン グエレメント5に対して放送することも可能である。以 上の接続を言い変えると、X座標が等しくてY座標が任 意のプロセシングエレメント5間がクロスバ・スイッチ で互いに接続されていることになる。プロセッサ間の接 続を図25に示す。プロッサ間の接続関係を表す行列を 図26に示す。行列において要素の値が1であるところ に接続関係がある。

18

【0083】以上の結合は図27に示すハイパーキュー ブ接合を包含する強力な結合である。

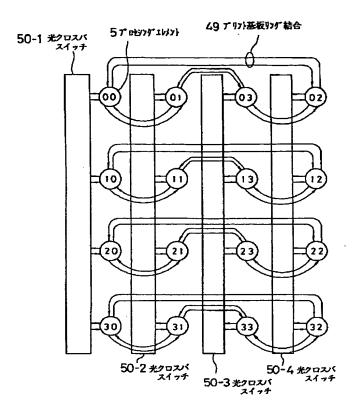

【0084】図28はハイパーキューブのプロセッサ間 の接続関係を表す行列であるが、図28において1であ る要素は全て図26において1であることから明かであ る。ハイパーキューブ結合では全ての値が0になる部分 行列ができるが、基板が多くなった場合は本発明を適用 した結合にくらべて全ての値が0になる部分行列の数が プロセシングエレメントが多いほど多くなるため結合網 の性能の差は更に広がる。

【0085】またバックプレインを用いたハイパーキュ ープ結合は基板の枚数が多くなるほど実装が困難になる が、本発明の場合は基板の枚数の制限は緩いのでプロセ シングエレメントが多くてもハイパーキュープ以上の能 力を持つ結合網が容易に実装できる。

【0086】また光を用いているので電気による通信路 に比べてノイズや通信路間の干渉、インピーダンス不整 合による反射、接地電位の不整合などの悪影響が少ない ため信頼性が高く、転送速度を容易に高速化することが 30 可能である。

【0087】次にハイパーキューブの通信パターンの動 作を通して、制御メモリを用いた本実施例の結合網の動 作方法を説明する。図27のハイパーキューブにおい て、全プロセシングエレメントが隣接する4つのプロセ シングエレメント5間で4つのメッセージを送信し4つ のメッセージを受信する動作を繰り返すことを、本実施 例の結合網で模擬するとする。ここで各プロセシングエ レメント5は1つのメッセージの送信と1つのメッセー ジの受信を同時に行う能力を持つものとする。

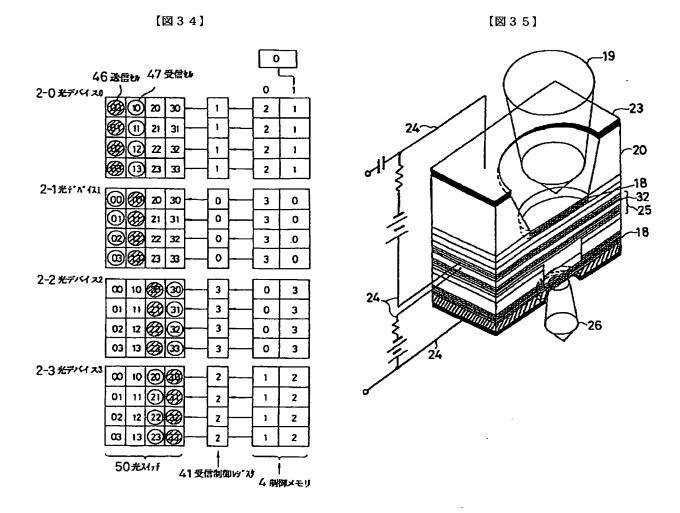

【0088】この動作をさせるには図29、図30、図 31、図32に示す4回の通信を行えば良い。これらの 図中の点線は基板を意味するので、図29、図30の通 信は基板内のリング(二次元ハイパーキューブ)結合網 で行い、図31、図32の通信は基板間通信になるので 光クロスバ結合網で行う。

【0089】光クロスパ網を用いる通信においては各プ ロセシングエレメントについてメッセージを受信すべき 相手のプロセシングエレメントのY座標(基板アドレ

【0090】例えば図31の通信においてPE005-00はPE205-20のメッセージを受信するのでPE005-00の受信用制御メモリには2を記憶させる。逆にPE205-20はPE005-00からのメッセージを受信するのでPE205-20の受信用制御メモリには0を記憶させる。以上のようにして図31、図32に対応する制御メモリの内容は図33のアドレス0、アドレス1に示すようにプログラムされる。

19

【0091】図33ではアドレス0のパターンが制御レ 10 信が実現できる。 ジスタ41に読み出され図31の通信ができるような状 【0099】また 態になっている。番号が斜線で塗りつぶされたセルは通 配列したデバイス 信が選択されているセルで、番号が〇で囲まれたセルは り、容易に素子能 受信が選択されたセルを意味する。 を実現できる。し

【0092】図34ではアドレス1のパターンが制御レジスタ41に読み出され図32の通信ができるような状態になっている。このようにアドレスを0,1,0,1とループさせて読み出せばハイパーキューブの通信を繰り返し行うことが可能であり、切り換えにおいては調停がないので高速である。またこの例のように全ての光パ20スが効率的に使われるように制御できるので、転送能力を極限まで引き出すことが可能である。

【0093】なお本実施例では制御メモリはプロセシングエレメントとは別に設けてあるが各プロセシングエレメントが自分の受信制御情報をローカルメモリに持ち、送信リンクを使って光デバイス内の制御レジスタに書き込んで受信選択を行っても良い。

【0094】以上の実施例では簡単のため基板内プロセシングエレメント数4、基板枚数4の並列計算機を示したが、現在の半導体集積技術は高性能なプロセシングエ 30 レメントを数センチメートル四方に実装することを可能にしているので、基板内に百台規模の高性能なプロセシングエレメントを搭載することは現時点でも可能である。

【0095】また直径数ミクロン程度の面発光レーザや MQW素子が製作されているので万のオーダーの規模の 光セルを実現できる可能性がある。ゆえに万のオーダー のプロセシングエレメント間をクロスバ網に近い結合網 で結合できる可能性がある。現在の光通信技術では1本 あたり数百メガビット/秒から1ギガビット/秒程度の 40 通信速度は比較的容易に実現できるようになってきているので、テラビット/秒を越える基板間総合転送速度を 実現できる可能性がある。

【0096】また切り換え速度の面からみてもMQWなどの半導体光素子を用いて構成することが可能なのでナノ秒を下回る速度で切り換えることも原理的に可能であり、従来の手動や液晶などを用いた光学的なスイッチに比べて飛躍的に高速な切り換えを可能にする。

【0097】また本発明は並列計算機のプロセッサ間結 合網のみでなく、ディジタル交換機などにも適用するこ 50 とができる。さらにその他の広範なディジタルシステム のバックプレインを置き換えるための技術として利用できる。バックプレインの代わりに本発明を適用した配線 を用いれば、結合できる基板の枚数の制約と基板間通信能力は飛躍的に改善され、その結合の柔軟な可変性から 汎用な基板間結合手段を提供することが可能になる。

[0098]

【発明の効果】以上説明したように本発明による光素子 を面型光素子アレイに用いると、容易に高性能基板光通 信が実現できる。

【0099】また、発光/受光素子をマトリックス状に配列したデバイスを用いて光バスを構成することにより、容易に素子間の結合が得られ、高速・高性能なバスを実現できる。しかも、前記デバイスは集積化技術を用いることにより、素子数の多いデバイスを作ることが可能なため、配線数を増加させてバスのフレキシビリティを向上させることができる。

【0100】また、本発明による光学式プロセッサ間結合網においては、電気式と比べ基板間転送周波数を高速化し、ノイズによる信頼性低下を抑制し、基板間配線本数を飛躍的に増加させることができる。さらに、少ないハードウェア量を用いて接続可能基板数を多くしたうえで、クロスバ網に近い密なトポロジーを持つ超並列計算機むけ結合網を高密度に構成することを可能にするとともに、従来の手動式や液晶式などに比べて高速に接続の切り換えが可能になるという効果が得られる。

【図面の簡単な説明】

【図1】本発明の一実施例の光素子の構成を示す図である。

【図2】リング状の光バスの構成を示す図である。

【図3】本発明の他の実施例の光素子の構成を示す図である。

【図4】ボード上に面状発光/受光デバイスが設けられている様子を示す図である。

【図5】ボード上の面状発光/受光デバイスを示す図で ある

【図6】各ポードを介してプロセッサが通信する様子を 示す図である。

【図7】受光素子の受信の様子を示す図である。

【図8】 受光素子の受信の様子を示す図である。

【図9】受光素子の受信の様子を示す図である。

【図10】本発明の第3実施例に係わる並列光リングバスを具備する並列計算機の光学式プロセッサ間結合網の構成を示す模擬図(概略図)である。

【図11】4箇所のミラーとミラーの間に基板を多数配置した並列光リングバスを具備する並列計算機のプロセッサ間結合網の概略を示した図である。

【図12】本発明の第4実施例に係わる光デバイスの構成を示した図である。

【図13】本発明の第5実施例に係わる光素子群セルの

構成を示す図である。

【図14】中継素子の断面図を示す。

【図15】図13のA-B線に沿った光デバイスを適用 した受信素子の断面図を示す。

【図16】送信素子の断面図を示す。

【図17】受信素子の下をくぐり抜けるように帯状の光 電変換素子を配置した受信部を示す。

【図18】帯状光電変換素子を用いた受信部を図17の 点C-Dによって切った断面図を示す。

【図19】送信と中継を兼用とする素子の断面図を示す。

【図20】複数のデバイス間の光のやりとりの形態を示した図である。

【図21】素子群の面積が小さいとき基板間の多少のズ レが許容されることを示した図である。

【図22】穴の空いた板を示す図である。

【図23】光を分岐させ受信素子と中継素子に導く様子 を示した図である。

【図24】各プロセシングエレメントに対応する送信セルと受信セルの位置の設定例を示す図である。

【図25】図21の設定をした場合のプロセッサ間の説明を示す図である。

【図26】図21の設定をした場合のプロセッサ間の接 続関係を表す行列である。

【図27】ハイパーキューブ結合のプロセッサ間の接続を示す図である。

【図28】ハイパーキューブ結合のプロセッサ間の接続 関係を表す行列である。

【図29】ハイパーキューブ結合の隣接プロセッサ間通信の第一のパターンを示す図である。

【図30】ハイパーキューブ結合の隣接プロセッサ間通信の第二のパターンを示す図である。

【図31】ハイパーキューブ結合の隣接プロセッサ間の 通信の第三のパターンを示す図である。

【図32】ハイパーキューブ結合の隣接プロセッサ間の 通信の第四のパターンを示す図である。

【図33】図31の通信パターンを実現する制御プログラムを読みだした状態を示す図である。

【図34】図32の通信パターンを実現する制御プログラムを読みだした状態を示す図である。

【図35】GaAlAs/GaAs系、InGaAs/InAsp系、InGaAs/InAlAs系面型発光 レーザ素子並びにADP超格子積層膜素子構造を示す図 である。

【図36】プロセッサーボード中央部に位置する面型発光機能素子発光の変調情報光の配光による受光エリアの広がりと、各ボード間隙並びに隣接セル内の受光素子への影響を示す説明図である。

【図37】従来の超並列コンピュータのパスを示す図である。

【図38】従来の発光素子と受光素子を同一半導体基板上に集積化した例を示す図である。

【図39】ボード相互の位置をずらして配置した場合を 示す図である。

【図40】デバイス上の素子を密度を減らし、かつ出射 光88の放射角を広げることにより、素子相互の結合を 行う場合を示す図である。

#### 【符号の説明】

1-0 基板(プロセッサーボード)0

10 1-1 基板 (プロセッサーボード) 1

1-2 基板 (プロセッサーボード) 2

1-3 基板(プロセッサーボード)3

1-4 基板 (プロセッサーボード) 4

1-5 基板(プロセッサーボード) 51-6 基板(プロセッサーボード) 6

1-7 基板 (プロセッサーボード) 7

2-0 光デバイス0

2-1 光デバイス1

2-2 光デバイス2

20 2-3 光デバイス3

2-4 光デバイス4

2-5 光デバイス5

2-6 光デバイス6

2-7 光デバイス7

3-1 ミラー1

3-2 = 5-2 3-3 = 5-3

3-4 ミラー4

4-0 制御メモリ0

30 4-1 制御メモリ1

4-2 制御メモリ2

4-3 制御メモリ3

5-00 プロセシングエレメントPE00

5-01 プロセシングエレメントPE01

5-02 プロセシングエレメントPE02

5-03 プロセシングエレメントPE03

5-10 プロセシングエレメントPE10

5-11 プロセシングエレメントPE11

5-12 プロセシングエレメントPE12

40 5-13 プロセシングエレメントPE13

5-20 プロセシングエレメントPE20 5-21 プロセシングエレメントPE21

5-22 プロセシングエレメントPE22

5-23 プロセシングエレメントPE23 5-30 プロセシングエレメントPE30

5-31 プロセシングエレメントPE31

3-31 JUEJJOHUNJELES.

5-32 プロセシングエレメントPE32 5-33 プロセシングエレメントPE33

6-0 電気回路 0

50 6-1 電気回路1

26 光出力

| 23                                    | 24                                 |

|---------------------------------------|------------------------------------|

| 6-2 電気回路 2                            | 27 送信中継兼用素子                        |

| 6-3 電気回路 3                            | 28 帯状光電変換素子                        |

| 7 導波路型合波器                             | 2 9 出力回路                           |

| 8 光電変換                                | 30-1 レンズ1                          |

| 9-00 光セル00                            | 30-2 レンズ2                          |

| 9-10 光セル10                            | 30-3 レンズ3                          |

| 9-20 光セル20                            | 30-4 レンズ4                          |

| 9-30 光セル30                            | 30-5 レンズ5                          |

| 9-01 光セル01                            | 30-6 レンズ6                          |

| 9-21 光セル21                            | 10 30-7 レンズ7                       |

| 9-31 光セル31                            | 30-8 レンズ8                          |

| 9-02 光セル02                            | 31 全反射ミラー                          |

| 9-12 光セル12                            | 32 光スイッチ                           |

| 9-22 光セル22                            | 33 送信用電極                           |

| 9-32 光セル32                            | 34 中継制御電極                          |

| 9-03 光セル03                            | 3 6 導波路                            |

| 9-13 光セル13                            | 37 ハーフミラー                          |

| 9-23 光セル23                            | 38 光電変換層                           |

| 9-33 光セル33                            | 39 隣のセルの光素子群                       |

| 10-0 制御入力0                            | 20 40 光路                           |

| 10-1 制御入力1                            | 41 受信制御レジスタ                        |

| 10-2 制御入力2                            | 4 2 冷却水                            |

| 10-3 制御入力3                            | 43 穴                               |

| 11-0 データ入力0                           | 4.4 冷却水通路                          |

| 11-1 データ入力1                           | 4.5 金属板                            |

| 11-2 データ入力2                           | 4.6 送信セル                           |

| 11-3 データ入力3                           | 47 受信セル                            |

| 12-0 データ出力0                           | 48 回折角                             |

| 12-1 データ出力1                           | 49 プリント基板リング結合                     |

| 12-2 データ出力2                           | 30 50 光クロスパスイッチ群                   |

| 12-3 データ出力3                           | 50-1 光クロスパスイッチ群                    |

| 13 送信素子(LD、LED、ADP)                   | 50-2 光クロスパスイッチ群                    |

| 14 中継素子                               | 50-3 光クロスパスイッチ群<br>50-4 光クロスパスイッチ群 |

| 15 受信素子<br>16 受信データ導波路                |                                    |

| 10 受信アーク等仮路 17 受光エリア                  | 5 1 半導体基板<br>5 2 発光・透過素子           |

| 17 交元エリア<br>17-1 基準となる受光エリア           | 53 受光素子                            |

| 17-1 歴中とはる支ルエック 17-2 基板がずれている場合の受光エリア | 5 4 活性層                            |

| 18 高反射率多層膜                            | 5 6 - 1 ~ 5 6 - n ボード              |

| 19 光入力                                | 40 57-1~57-n 面状発光/受光デバイス           |

| 20 光デバイス基板                            | 65, 66-1, 66-2 マイクロプロセッサ           |

| 21 活性領域                               | 68-1~68-m 受光素子                     |

| 2.2 反射面                               | 69-1~69-m 信号検出器                    |

| 23 反射鏡電極                              | 70 スイッチ制御器                         |

| 2 4 制御電極                              | 7 1 スイッチ                           |

| 25 マスク層                               | 72-1~77-m 復号器                      |

|                                       | 7 2 1 1 11 11 12 7 mm              |

7 3 選択器

【8図】

[図10]

【図11】

【図12】 【図13】 10 制御入力 11;\*- 引入力 6-0 10-0 11-0 (デーナ入カウ)-制御 都回虎部 9-10 9-20 9-30 14 中継来子(図J4条照) / (JiQII) 4cr30 7 等被路型合波器 光母交换 一个 十出力的 15 受信未子 13 送信案于(図以学恩) (LiborLED) 6-1 10-1 (戦輝 (入力) (MOA) 11-1 *(*የ'*ተአጋ*ክ)\_ 花回戌即 9-21 9-11 9-01 9-31 17 受光功7 **t1**01 **ts**11 **1**121 **10**31 7.導被路型合放器 图 15 参照 s16 受信?" / 導波路 元母変換 \_\_12-1 (デーナ出カル) 6-2 10-2 (制御) 人力2 11-2 (デー<del>)</del>入力なー 超気回路 9-02 9-12 9-22 9,-32 В £#32 7 事效路型合被器 光電家換 12-2 6-3 11-3 6'-<del>ነ</del>ኢታኔ 10-3 (制御 ) (人力3) 包包回路 9-23 9-33 7 導放路型合放器 **Ł833** ₹¥13

17 受光功7

【図17】

【図30】

【図25】

【図26】

| _, | _ |   |   |   |   |   |   |   |   |   |    |   | $\neg$ |   |   |   |   |  |

|----|---|---|---|---|---|---|---|---|---|---|----|---|--------|---|---|---|---|--|

| j  | У | 0 |   |   |   | 1 |   |   |   |   |    | 2 |        | 3 |   |   |   |  |

| у  | × | 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2      | 0 | ì | 3 | 2 |  |

|    | 0 | 1 | - |   | 1 | 1 |   |   |   | _ |    |   |        | 1 |   |   |   |  |

| 0  | 1 | 1 | 1 | 1 |   | Г | ı |   |   |   | ī  |   |        |   | 1 |   |   |  |

|    | 3 | П | 7 | 1 | 1 | П |   | ī |   |   |    | 1 |        |   | · | 1 |   |  |

|    | 2 | 1 |   | 1 | ī |   | Г |   | 1 |   |    |   | =      |   |   |   | 1 |  |

|    | 0 | 1 |   |   |   | 1 | 1 |   | 1 | 7 |    |   |        | - |   |   |   |  |

|    | ī |   | 1 |   |   | 1 | 1 | , |   |   | 1  |   |        |   | 1 |   |   |  |

| 3  | 3 | Г | Γ | 1 |   |   | 1 | 1 | 1 |   | Γ. | 1 |        |   |   | 1 |   |  |

|    | 2 |   |   |   | 1 | 1 | Γ | ī | 1 | Γ |    | Г | 1      |   |   |   | 1 |  |

|    | 0 | 1 | Γ | Γ | Γ | 1 |   |   | Γ | 1 | 1  |   | 1      | ı |   |   |   |  |

| ١_ | ī | Г | 1 | Γ |   | Γ | 1 | Γ | Γ | 1 | 1  | ī |        |   | 1 |   |   |  |

| 2  | 3 |   |   | 1 | Г | Γ |   | 1 |   |   | 1  | 1 | 1      |   |   | 1 |   |  |

|    | 2 |   |   |   | 1 | Γ |   | Γ | ī | 1 | Γ. | 1 | 1      |   |   |   | 1 |  |

|    | 0 | 1 | Γ | Γ |   | 1 |   | Π |   | 1 |    |   |        | 1 | 1 |   | 1 |  |

| _  | 1 |   | 1 | Π | Π | Π | 1 |   |   |   | 1  |   |        | 1 | 1 | 1 |   |  |

| 3  | 3 |   | Γ | ī |   |   |   | 1 |   |   |    | 1 | L      |   | 1 | 1 | 1 |  |

|    | 2 |   |   |   | 1 |   |   |   | 1 |   |    |   | j      | 1 |   | 1 | l |  |

【図27】

【図28】

|   | у | 0 |    |   |   | 1  |   |   |   |   |   |   |   | 3 |   |   |   |

|---|---|---|----|---|---|----|---|---|---|---|---|---|---|---|---|---|---|

| у | x | 0 | 1  | 3 | 2 | 0  | 1 | 3 | 2 | 0 | ı | 3 | 2 | 0 | 1 |   | 2 |

|   | 0 | 1 | 1  |   | ı | 1  |   |   |   | 1 |   |   |   |   |   |   |   |

| 0 | 1 | 1 | 1  | 1 |   |    | 1 |   |   | ļ | 1 |   |   |   |   |   |   |

|   | 3 |   | 1  | 7 | 1 | l  |   | 1 |   |   |   | 1 |   |   |   |   |   |

|   | 2 | 1 |    | 1 | 1 | L  |   |   | 1 |   |   |   | i |   |   |   |   |

|   | 0 | 1 |    |   |   | ١  | 1 |   | 1 |   |   |   |   | 1 |   |   |   |

| , | 1 | ŀ | 1  |   |   | 1  | 1 | 3 |   |   |   |   |   |   | 1 |   |   |

|   | 3 |   |    | 1 |   |    | 1 | 1 | ı |   |   |   |   |   |   | t |   |

| L | 2 | L |    |   | 1 | 1  |   | 1 | 1 | L |   |   |   | L |   | _ | 1 |

| 2 | 0 | 1 |    |   |   | Ì  |   |   |   | 1 | 1 |   | 1 | 1 |   |   |   |

|   | 1 |   | ١. |   |   | l  |   |   |   | 1 | 1 | 1 |   |   | 1 |   |   |

|   | 3 |   |    | 1 |   |    |   |   |   | İ | 1 | 1 | 1 |   |   | 1 |   |

|   | 2 | L | _  |   | 1 | L  |   |   |   | 1 |   | 1 | 1 | L |   |   | 1 |

|   | 0 |   |    |   |   | יו |   |   |   | 1 |   |   |   | 1 | ì |   | 1 |

| 3 | 1 |   |    |   |   |    | 1 |   |   |   | 1 |   |   | 1 | 1 | 1 |   |

|   | 3 |   |    |   |   |    |   | 1 |   |   |   | 1 |   |   | ĭ | 1 | 1 |

| L | 2 |   |    |   |   |    |   |   | 1 |   |   |   | 1 | 1 |   | 1 | 1 |

【図32】 【図33】 O. (10) (01) 受信い 送信切 2-0 光デバイス0 20) 30 2 (12) 2 2 31 2 12 2 32 2 2 2 (31) **(23)** 33 1 (21) 2-1 光デバイス1 00 869 20 30 3 3 0 01 🐼 21 (33) (32 ③ 3 3 0 02 8 22 3 0 3 3 3 2-2 光デバイス2 (3) 10 0 0 【図37】 11 23 31 0 0 3 0 0 3 33 0 0 3 2-3光デバイス3 **∞** (10) **20 33** 1 01 (1) 21 (33) 82-1 2 02 (12) 22 (23) 1 2 50 光クロスバ 41 受信制御りつな 4 制御代り 81

【図36】

フロントページの続き

(72)発明者 田邊 昇

神奈川県川崎市幸区小向東芝町 1 株式会 社東芝総合研究所内 (72)発明者 関戸 一紀

神奈川県川崎市幸区小向東芝町1 株式会 社東芝総合研究所内 (72)発明者 上西 克二 神奈川県川崎市幸区小向東芝町1 株式会 社東芝総合研究所内